# Vokasi Unesa Bulletin of Engineering, Technology and Applied Science (VUBETA) https://journal.unesa.ac.id/index.php/vubeta

Vol. 2, No. 2, 2025, pp. 243~251 DOI: 10.26740/vubeta.v2i2.37172 ISSN: 3064-0768

# Simulation and Experimental Evaluation of a 5-Level Cascaded H-Bridge Inverter

Mahmud Ismaila<sup>1</sup>, Sulaiman Haruna Sulaiman<sup>2</sup>, Abdulwahab Ibrahim<sup>3\*</sup>, Ibrahim Abdullahi Shehu<sup>4</sup>, Musa Mohammed<sup>5</sup>

1,2,3,4,5, Department of Electrical Engineering, Faculty of Engineering, Ahmadu Bello University, Zaria-Nigeria

### **Article Info**

### Article history:

Received December 20, 2024 Revised February 23, 2025 Accepted February 25, 2025

# Keywords:

Multilevel Inverter Pulse Width Modulation Switches Total Harmonic Voltage Output

#### **ABSTRACT**

Multilevel inverters (MIs) are designed in such a way that different DC sources could be used to achieve the desired output voltage. This includes high quality output voltage, reduction of voltage stress on the switches, low common mode voltages, lower harmonic content and reduction in the total harmonic distortion compared to the conventional voltage source inverter. As there will be reduction in THD, the size of the filter will also get minimized thereby decreasing the system complexity. Sinusoidal pulse width modulation technique is commonly employed in MIs in order to obtain undistorted output voltage by eliminating lower order harmonics. Cascaded H-bridge MIs are the most preferable for this purpose due to their modularity, reliability, less usage of clamping diodes and ease of control of circuitry and it also reduces the switching and conduction losses of the system. In this study, 5-level cascaded H-bridge inverter was simulated in MATLAB/Simulink software environment. A prototype of the simulated 5-level inverter was also constructed, and the result was compared with that obtained from simulation. The results of both the simulation and experimental measurement have a similar output voltage waveform and the THD value of 33.12% and 33% for the simulation and experiment respectively.

This is an open access article under the CC BY-SA license.

# 1. INTRODUCTION

Multilevel inverters (MIs) are gaining attention and have emerged as an important technology in the field of power electronics, playing a critical function of converting direct current (DC) to alternating current (AC) with high efficiency and superior output waveform quality [1]. Unlike traditional two-level inverters that produce a binary voltage output, multilevel inverters generate a stepped waveform that closely approximates a sinusoidal wave, resulting in reduced harmonic distortion and lower electromagnetic interference [2]. An MI is a power electronic device designed to synthesize a desired AC voltage output from several DC voltage sources. Unlike traditional two-level inverters that produce a square wave output with two distinct voltage levels, MIs generate a more sinusoidal output by utilizing a number of voltage levels. In this way, harmonic distortion is reduced and the overall quality of the output waveform is enhanced [3][4].

Renewable energy sources (RES) such as solar photovoltaic (PV) and wind are increasingly being used in the supply of the ever-growing electricity demand resulting, in part, from urbanization [5][6]. Solar PV generates DC power which needs to be converted into AC for most applications [7][8]. This can be achieved using cascaded H-bridge MIs with low total harmonic distortion (THD). The performance of such inverters is generally analyzed based on their output active power, reactive power as well as the THD level in the output voltage. There are two main classes of MIs namely current source inverter (CSI) and voltage source inverter [9][10]. The CSI has a drawback of high fault current capable of damaging the connected appliance or equipment whenever a short circuit occurs. Hence, multilevel VSIs are more commonly employed than the CSI in high power applications. Multilevel VSIs are further classified into three main categories namely cascaded H-bridge (CHB), Neutral point clamped (NPC) and Flying capacitor (FC) Mis [11]. Among all the

\*Corresponding Author

Email: iabdulwahabb@gmail.com

three, Cascaded H-bridge MI is more widely due its numerous capabilities. Hence, it is the focus of this paper. CHBs have been identified to have a wide area of industrial applications due to their high reliability, efficiency, scalability, flexibility, high output voltage, and ease of control. In all such applications, the main aim is to provide a higher operation efficiency. Some of such applications are concisely described below [12]-[14]:

**Electric vehicles**- due to their high efficiency and reliability, CHBs are usually employed in the development of high-power charging stations for EVs in order to achieve increased efficiency through fast charging. They can also be used for propulsion purposes in the EVs.

**Motor Drives** – multi level CHBs can be adapted to motor drives in variety of areas such as multi-motor control, high-torque applications. They can also be integrated with advance control algorithms such as model predictive control.

**Renewable Energy Systems**- Multi-level CHB inverters are also used in RES such as solar and wind for the efficient conversion of DC power to AC before feeding it to the grid.

The CHBs can also be used in Uninterruptible power supplies (UPS) and Power quality improvement- in order to provide stable power supply, reduce harmonics and enhance grid stability.

# 1.1. Literature Review

Several researches have been carried out in the area of multilevel inverters. The authors in [3] focused on five level cascaded H-bridge MI having small number of switches using sinusoidal pulse width modulation (SPWM) and carried out simulation of the multilevel inverter on a MATLAB/SIMULINK. A prototype of the inverter was also constructed and the output waveform was monitored and measured using an oscilloscope. The constructed inverter was found to have higher quality output waveform compared to conventional DC to AC inverter. A 7-level cascaded H-Bridge MI, based on SPWM and multicarrier sinusoidal pulse width modulation (MSPWM) strategies, was designed and constructed in [15]. The output waveforms of the two strategies were observed both on proteus software and an oscilloscope. The results, in terms of THD, before and after filtering were compared. It was clear that the THD obtained in the MSPWM technique was lower than that of the SPWM technique with a value of 18.3% and 24.93% respectively. A model of 5-level cascaded H-bridge MI with three and six phase voltages were developed by [16]. The simulation results with respect to THD show that the six-phase 5-level inverter is slightly similar to the three-phase 5-level inverter with value of 16.02% and 16.05% respectively. The 2-level inverter has the advantage of low weight and cost compared to the other topologies. However, it is non-practical due to the high THD associated with its output voltage. The design of the 5-level MI, on the other hand, seems to be more optimal than that of 9-level MIs. This can be associated with the increased cost and weight that are proportional to the number of levels in the inverter. Hence, this topology is good for industrial drives applications. The work in [17] involved simulation-based investigation of the voltage performance of some distinct three-phase 5-level CHMI with different numbers of switches and DC sources. The results show that the inverter with eight switches has the highest THD value of 38.82% while the inverter with five switches and two DC sources has the least value of THD of 21.95%.

# 2. THEORETICAL BACKGROUND

### 2.1. Multilevel Inverter

Multilevel inverters were introduced in 1975 beginning with the three-level and other multilevel topologies were subsequently developed [17]. Generally, the primary function of a multilevel inverter is to ensure higher power through the use of series of power semiconductor switches alongside several lower voltage dc sources which perform the power conversion through synthesis of a staircase voltage waveform [18]. In modern electrical engineering and power electronics, multilevel inverters have become an essential technology for efficient and reliable power conversion. These inverters, that can produce multiple voltage levels, offer significant advantages over traditional two-level inverters, especially in high-power and high-voltage applications. The growing demand for renewable energy integration, industrial drives, and electric vehicles underscores the importance of advanced inverter technologies, making multilevel inverters a focal point of research and development.

Among the different types of inverters, MIs are of particular interest because of their high-quality AC waveforms production capability. Unlike traditional two-level inverters, which switch between two voltage levels, MIs use multiple voltage levels to synthesize a more sinusoidal output. This results in improved power quality, higher efficiency, and lower electromagnetic interference [19]. There are several types of multilevel inverters, each with its unique topology and operational characteristics over the last two decades. Contemporary research has engaged novel converter topologies employing unique modulation techniques. three major multilevel inverters topologies have been reported in the literature as discusses below:

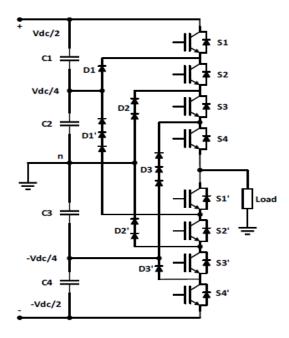

### 2.2.1. A. Diode-Clamped Multilevel Inverters (DCMLI)

These inverters, depicted in Figure 1, are also called Neutral Point Clamped (NPC) inverters, use diodes to clamp the voltage levels, providing a straightforward design suitable for medium voltage applications. They are employed in medium to high voltage applications due to their ability to generate multiple voltage levels with reduced harmonic distortion [11]. DCMLIs are designed to produce a staircase waveform with multiple voltage levels. A typical three-level NPC inverter has three voltage levels (Vdc, 0, and -Vdc). The key feature of this topology is the use of clamping diodes to fix the intermediate voltage levels, ensuring that the voltage stress on each power device is limited to a single voltage level (Vdc). Figure 1 depicts an NPC inverter.

Figure 1. Neutral Point Clamped (NPC) Inverter Topology

# 2.2.2. Flying Capacitor Multilevel Inverter (FCMLI)

FCMLIs use capacitors to produce multiple output voltage levels. This topology is known for its modularity and capability to produce high-quality output waveforms with less THD. FCMLIs produce a staircase waveform with multiple voltage levels. the number of capacitors and switches used in the design determine the number of voltage levels of the inverter. The capacitors are charged to specific voltages to create the required output levels.

Insulated Gate Bipolar Transistors (IGBTs) and Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) are mostly used for the switching operations in FCMLI. These capacitors are used to generate intermediate voltage levels. They are placed between the power switches and are crucial for voltage balancing. The inverter operates by switching the power devices in a specific sequence to charge and discharge the flying capacitors, thus generating the desired output voltage levels. For an n-level FCMLI, (n-1) capacitors are required. Each capacitor is charged to a fraction of the total DC voltage, creating intermediate voltage levels.

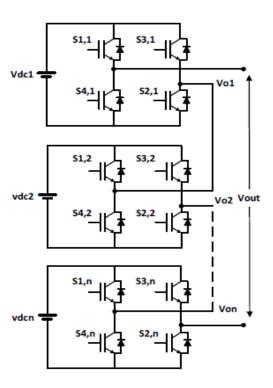

# 2.2.3. Cascaded H-Bridge (CHB) Multilevel Inverter

Cascaded H-bridge inverters are particularly noted for their modularity and ability to produce high-quality waveforms with reduced harmonic distortion [6]. The basic building block of this inverter type is the H-bridge cell, that consists of four switches that are typically either transistors or IGBTs arranged in an "H" configuration. Each H-bridge cell can produce three voltage levels: positive, negative, and zero. Figure 2 depicts an n-level CHB inverter topology. Each H-bridge cell is connected to a particular isolated DC voltage source which could be batteries, solar panels, or other DC power supplies. A control system manages the switching of the H-bridge cells to produce the desired AC output waveform.

Multiple H-bridge cells are connected in series, and their outputs are combined to form the overall output voltage of the inverter (Figure 2). By controlling the switching of each cell, the inverter can produce a stepped approximation of a sinusoidal waveform. The inverter achieves high-quality AC output by synthesizing the desired waveform through pulse-width modulation (PWM) or other modulation techniques. The more H-bridge cells used, the closer the output waveform can approximate a pure sine wave, reducing harmonic distortion. The main advantage of the CHB inverter is its ability to produce a multilevel output voltage. This

allows for higher voltage operation with lower THD compared to the conventional two-level inverters [15, 20-22].

The ratio of all harmonic components to the fundamental component is known as THD [23]. Total voltage harmonic distortion (THD<sub>v</sub>) is expresses in equation 1 [24].

$$THD_{v} = \frac{1}{V_{1}} \left[ \sum_{h=2}^{\infty} V_{h}^{2} \right]^{1/2} \tag{1}$$

Where,  $V_l$  and  $V_h$  represent the rms value of fundamental and  $h^{th}$  harmonic components of the voltage respectively.

Figure 2. Cascaded H-bridge Multilevel Inverter Topology

# 3. METHODOLOGY

This section presents the method used in designing the five-level CHB inverter via simulation and experiment.

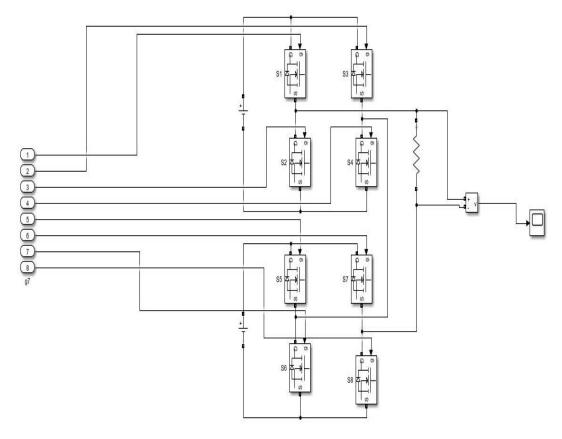

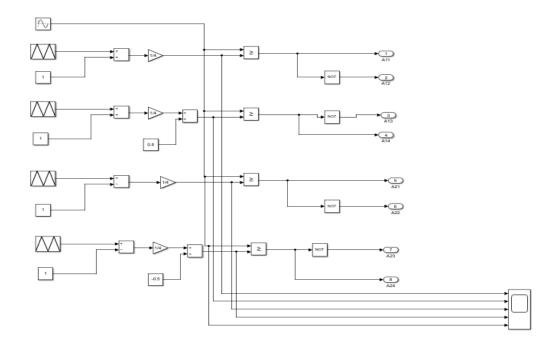

# 3.1. MATLAB/SIMULINK DESIGN

The designed inverter model is simulated using MATLAB/Simulink. The 5-level CHB inverter consists of two H-bridge cells connected in series, each powered by independent DC voltage sources. For generating five voltage levels, two H-bridge cells are needed, each capable of producing three voltage levels (-V, 0, +V). The five-level CHB inverter is modeled along with a PWM. Eight switches are used with two DC sources. The parameters for PWM and the 5-level CHB inverter are provided in Table 1. The Simulink model of 5level CHB is shown in Figure 3, while Figure 4 shows the Simulink model for the SPWM that will drive the 5-level CHB inverter.

Table 1. Simulation specification for the 5-level CHB inverter

| Specification                                         | Value |

|-------------------------------------------------------|-------|

| Rated inverter output frequency Modulating frequency) | 50Hz  |

| Dc link voltage of H-bridge                           | 12V   |

| Carrier frequency (f <sub>c</sub> )                   | 100Hz |

The 5-level CHB inverter model has eight switching transistors to produces the 5-level output voltage of the inverter. A gate signal generation unit is required to drive the inverter. Sinusoidal pulse width modulation (SPWM) is used in generating the gate signals for the inverter as shown in Figure 4.

Figure 3. Simulink Model of Five-level CHB Inverter

Figure 4: SPWM model

# 3.2. Five-Level CHB Inverter Prototype Design

The validation of the simulation is done by constructing a prototype with eight MOSFET transistors as switches, the gating signal are generated through a microcontroller and opto-coupler. Other components are carefully selected to ensure that the inverter operates efficiently and meets system requirements. After considering the parameters used in the simulation, the following components were selected to construct the inverter as indicated in Table 2.

| Components           | Rating     |

|----------------------|------------|

| MOSFET               | 4N60       |

| Microcontroller [25] | 16F877A    |

| Diodes               | 1N4001     |

| Capacitor            | 1000uF 25V |

| Transformer          | 12V *2     |

| Resistor             | 1Ω         |

| Crystal oscillator   | 16mHz      |

| Opto-coupler         | TLP250     |

| Voltage regulator    | 7805       |

Table 2. Components Specifications

### 4. RESULTS AND DISCUSSION

**LEDs**

The construction of a 5-level cascaded H-Bridge multilevel inverter involves several key components and subsystems that work together to convert DC power into high-quality AC output with multiple voltage levels. The following are detailed results obtained from the simulation and construction of the inverter.

1.8V

#### 4.1. Simulation Results

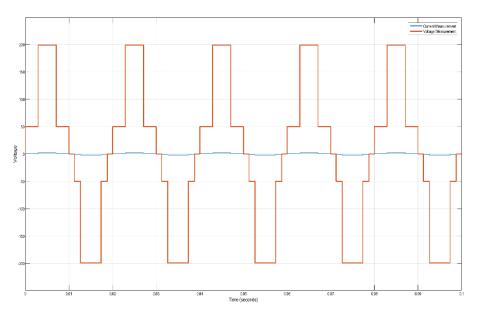

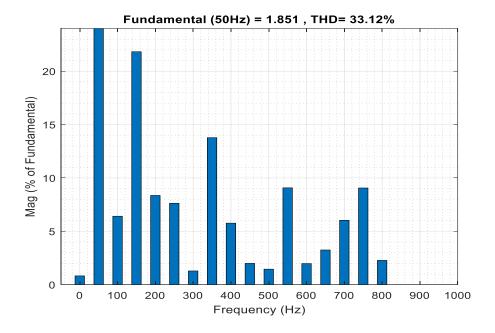

The simulation of the 5-level cascaded H-Bridge inverter was performed using MATLAB/Simulink. The voltage output waveform of the inverter is as shown in Figure 5 and the total harmonic distortion (THD) results was found to 33.12% as depicted in Figure 6.

Figure 5. Voltage output waveform of the five-level Inverter

.

Figure 6. THD spectrum result of five-level CHB inverter

### **4.2.** Experimental Results

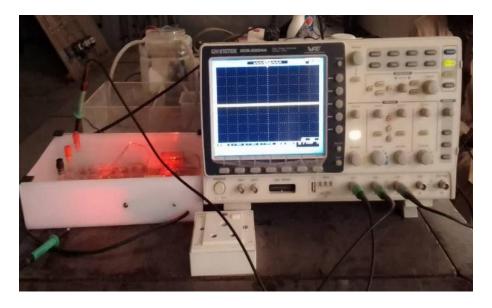

The hardware of the 5-level CHB inverter was constructed as shown in Figure 7. Testing was carried out using oscilloscope to capture the output of voltage waveform of the multilevel inverter and to also measure the THD of the prototype of the inverter.

Figure 7. Constructed Five-level CHB inverter prototype

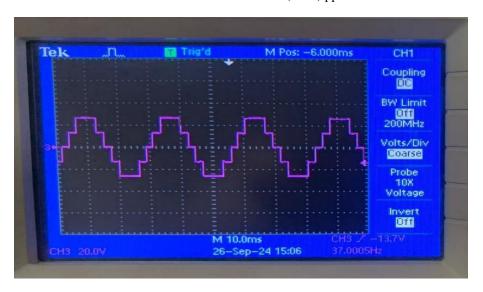

The results of the prototype inverter obtained from the oscilloscope show that a 5-level voltage output is produced by the inverter as shown in Figure 8 is similar to that produced in the simulation as depicted in Figure 5. The magnitude of the output voltage is 24V which correspond to the voltage value of the simulation model. THD measured from the oscilloscope for the prototype CHB inverter is found to be 10dB which is equivalent to 33% which is slightly similar to the simulation result in Figure 9 that has THD value of 33.12%.

Figure 8. Experimental Voltage Output Waveform of the 5-Level CHB Inverter

The developed hardware on cascaded H-bridge five level inverter using SPWM method has high quality output waveform compared to conventional direct current to alternative current inverter. From the result obtained above the total harmonic distortion of the simulated inverter is same as that of the constructed inverter. The THD is at 33% due to the microcontroller (16F877A) used, as it cannot produced more than 100 Hz carrier frequency. A higher carrier frequency will have less THD value. The main advantage of the cascaded H-bridge inverter is less cost and weight compared with other type inverters. This method is well suited for industry's drives. By having a less filter circuit in the network and still have less THD value. This circuit implementation decreases the usage of switches. The developed hardware is able to operate in both symmetrical and asymmetrical modes.

#### 5. CONCLUSION AND LIMITATION

This paper modeled a single phase 5-level cascaded H-Bridge multilevel inverter using MATLAB/Simulink and its prototype was also constructed. Results of both the simulation and experimental set-up were obtained and compared. The total harmonic distortion in the simulated inverter is closely similar to that of the constructed prototype. In both cases, the inverter has achieved significant reduction in THD value and an improved voltage of five level as compared to the 2-level produced by the conventional inverter. Microcontroller that can produce high carrier frequency could be adopted to improve in reducing THD value.

#### REFERENCES

- [1] R. K. Gatla *et al.*, "Comprehensive analysis of faults and diagnosis techniques in cascaded multi-level inverters," *Heliyon*, vol. 10, no. 21, 2024, https://doi.org/10.1016/j.heliyon.2024.e39901.

- [2] O. S. Vargas, S. E. D. L. Aldaco, J. A. Alquicira, L. G. Vela-Valdés, and A. R. L. Núñez, "Adaptive network-based fuzzy inference system (ANFIS) applied to inverters: a survey," *IEEE Transactions on Power Electronics*, vol. 39, no. 1, pp. 869-884, 2023, https://doi.org/10.1109/TPEL.2023.3327014.

- [3] A. Salem, H. Van Khang, K. G. Robbersmyr, M. Norambuena, and J. Rodriguez, "Voltage source multilevel inverters with reduced device count: Topological review and novel comparative factors," *IEEE transactions on power electronics*, vol. 36, no. 3, pp. 2720-2747, 2020, https://doi.org/10.1109/TPEL.2020.3011908.

- [4] B. Mosepele, R. Samikannu, and L. Amuhaya, "A structural review on reduced switch count and hybrid multilevel inverters," Frontiers in Energy Research, vol. 12, p. 1396149, 2024, https://doi.org/10.3389/fenrg.2024.1396149.

- [5] A. Hafis, A. S. Adamu, Y. Jibril, and I. Abdulwahab, "An Optimal Sizing of Small Hydro/PV/Diesel Generator Hybrid System for Sustainable Power Generation," *Journal of Engineering Science Technology Review*, vol. 16, no. 6, 2023, http://dx.doi.org/10.25103/jestr.166.01.

- [6] I. Abdulwahab, S. Faskari, T. Belgore, and T. Babaita, "An improved hybrid micro-grid load frequency control scheme for an autonomous system," *FUOYE Journal of Engineering Technology*, vol. 6, no. 4, pp. 369-374, 2021, http://dx.doi.org/10.46792/fuoyejet.v6i4.698.

- [7] S. Sulaiman, H *et al.*, "Investigation of Effect of Dust Accumulation on the Performance of Solar Photovoltaic Modules: A Case Study of Samaru, Zaria," *Nigerian Journal of Engineering*, vol. 31, no. 1, pp. 92-99, 2024, https://njeabu.com.ng/?mno=172569.

- [8] I. Abdulwahab et al., "Solar Irradiance Prediction for Zaria Town Using Different Machine Learning Models," Pakistan Journal of Engineering Technology, vol. 7, no. 2, pp. 66-71, 2024, http://dx.doi.org/10.51846/vol7iss2pp66-71.

.

- [9] M. Dogra, V. S. Sharma, A. Sachdeva, and J. Dureja, "TPM-a key strategy for productivity improvement in process industry," *Journal of Engineering Science Technology*, vol. 6, no. 1, pp. 1-16, 2011, https://jestec.taylors.edu.my/Vol%206%20Issue%201%20February%2011/Vol\_6\_1\_\_001\_016\_MANU%20DOGR A.pdf.

- [10] A. A. Khan, A. F. Minai, Q. Alam, and F. I. Bakhsh, "Multilevel Inverters: Classification, Approaches, and Its Application in Photovoltaic System," *Multilevel Converters*, pp. 27-50, 2024, http://dx.doi.org/10.1002/9781394167371.ch2.

- [11] R. Nagar, K. Shroff, A. Jagtap, N. B. Patil, and L. P. Patil, "A Survey on Conventional Multilevel Inverter Topologies," in *International Conference on Smart Computing and Communication*, pp. 249-262, 2024, https://doi.org/10.1007/978-981-97-1326-4\_21.

- [12] W. Wu, X. Liu, J. Liang, Z. Liu, and C. Huang, "Application of cascaded H-bridge multilevel inverter in the speed regulation of medium-and high-voltage asynchronous motor," *Journal of Power Electronics*, vol. 24, no. 3, pp. 391-413, 2024, https://doi.org/10.1007/s43236-023-00759-0.

- [13] S. Kamlu, "Comparative analysis for Cascaded H-Bridge Multilevel Inverter," in 2024 3rd International Conference for Innovation in Technology (INOCON), pp. 1-6, 2024, http://dx.doi.org/10.1109/INOCON60754.2024.10511338.

- [14] D. Narmitha, K. Karthikumar, P. Chandrasekar, and P. G. Sankar, "Cascaded H Bridge Inverter Fed Motor Drive for Electric Vehicle Applications," in 2024 10th International Conference on Electrical Energy Systems (ICEES), pp. 1-9, 2024, http://dx.doi.org/10.1109/ICEES61253.2024.10776852.

- [15] X. Guo, X. Wang, C. Wang, Z. Lu, C. Hua, and F. Blaabjerg, "Improved modulation strategy for singe-phase cascaded H-bridge multilevel inverter," *IEEE Transactions on Power Electronics*, vol. 37, no. 3, pp. 2470-2474, 2021, http://dx.doi.org/10.1109/TPEL.2021.3109982.

- [16] K. Jena *et al.*, "A novel three-phase switched-capacitor five-level multilevel inverter with reduced components and self-balancing ability," *Applied Sciences*, vol. 13, no. 3, p. 1713, 2023, https://doi.org/10.3390/app13031713.

- [17] M. Kavitha, A. Arunkumar, N. Gokulnath, and S. Arun, "New cascaded H-bridge multilevel inverter topology with reduced number of switches and sources," *IOSR-JEEE*, vol. 2, no. 6, pp. 26-36, 2012, https://doi.org/10.9790/1676-0262636

- [18] A. Bhanuchandar and B. K. Murthy, "A new generalized floor function based high switching frequency modulation and control technique: Multilevel inverters," *International Journal of Circuit Theory Applications*, vol. 51, no. 10, pp. 4754-4773, 2023, https://doi.org/10.1002/cta.3659.

- [19] I. Harbi *et al.*, "Model-predictive control of multilevel inverters: challenges, recent advances, and trends," *IEEE Transactions on Power Electronics*, vol. 38, no. 9, pp. 10845-10868, 2023, https://doi.org/10.1109/TPEL.2023.3288499.

- [20] I. Ahamad et al., "Performance assessment of solar energy driven cascaded H-bridge multilevel inverters," Microsystem Technologies, pp. 1-9, 2024, https://doi.org/10.1007/s00542-024-05748-2.

- [21] N. Agrawal, A. Agarwal, and T. Kanumuri, "Advanced PWM technique for power quality optimization in 5-level CHB inverter systems," *Electrical Engineering*, pp. 1-17, 2024, https://doi.org/10.1007/s00202-024-02869-9.

- [22] B. Sathyavani, K. S. Tara, and K. Sreedevi, "Modelling and Examination of Symmetric and Asymmetric CHB Inverter for Multiple Output Levels," in *Emerging Technologies & Applications in Electrical Engineering*: CRC Press, pp. 203-210, 2024, https://doi.org/10.1201/9781003505181-25.

- [23] R. Sarker, A. Datta, and S. Debnath, "An improved multicarrier PWM (MCPWM) technique with a new harmonic mitigation strategy for cascaded H-bridge multilevel inverter applications," *IEEE Transactions on Industrial Informatics*, vol. 18, no. 3, pp. 1500-1510, 2021. https://doi.org/10.1109/TII.2021.3087458.

- [24] A. Arranz-Gimon, D. Morinigo-Sotelo, A. Zorita-Lamadrid, and O. Duque-Perez, " IEEE Access, vol. 2024, 2024, https://doi.org/10.1109/ACCESS.2024.3474176.

- [25] M. C. Garcia, M. A. Sanz-Bobi, and J. Del Pico, "SIMAP: Intelligent System for Predictive Maintenance: Application to the health condition monitoring of a windturbine gearbox," *Computers in industry*, vol. 57, no. 6, pp. 552-568, 2006, https://doi.org/10.1016/j.compind.2006.02.011.